# Divisible Job Scheduling in Systems with Limited Memory

Paweł Wolniewicz

2003

## Table of Contents

| Ta | Table of Contents                |                                                |                                                     |    |  |  |  |

|----|----------------------------------|------------------------------------------------|-----------------------------------------------------|----|--|--|--|

| 1  | Intr                             | Introduction  Divisible Job Model Fundamentals |                                                     |    |  |  |  |

| 2  | Div                              |                                                |                                                     |    |  |  |  |

|    | 2.1                              | Formulation of the problem                     |                                                     |    |  |  |  |

|    | 2.2                              | System                                         | architecture                                        | 7  |  |  |  |

|    |                                  | 2.2.1                                          | Routing topologies                                  | 8  |  |  |  |

|    |                                  | 2.2.2                                          | Layer activation order                              | 13 |  |  |  |

|    |                                  | 2.2.3                                          | Single-installment and Multi-installment processing | 13 |  |  |  |

|    | 2.3                              | Survey                                         | of the Earlier Results                              | 16 |  |  |  |

| 3  | Systems with Single Memory Level |                                                |                                                     |    |  |  |  |

|    | 3.1                              | e v                                            |                                                     |    |  |  |  |

|    | 3.2                              | ·                                              |                                                     |    |  |  |  |

|    |                                  | 3.2.1                                          | Star                                                | 22 |  |  |  |

|    |                                  | 3.2.2                                          | Binomial trees                                      | 29 |  |  |  |

|    |                                  | 3.2.3                                          | Conclusions                                         | 37 |  |  |  |

|    | 3.3                              |                                                |                                                     |    |  |  |  |

|    |                                  | 3.3.1                                          | Linear programming approach                         | 38 |  |  |  |

|    |                                  | 3.3.2                                          | Branch and Bound algorithm                          | 40 |  |  |  |

|    |                                  | 3.3.3                                          | Heuristic algorithms                                | 42 |  |  |  |

|    |                                  | 3.3.4                                          | Computational experiments                           | 44 |  |  |  |

|    |                                  | 3.3.5                                          | Conclusions                                         | 54 |  |  |  |

| 4  | Sys                              | tems w                                         | rith Hierarchical Memory                            | 56 |  |  |  |

|    | 4.1                              | Mathematical Models                            |                                                     |    |  |  |  |

|    | 4.2                              | Performance Modeling                           |                                                     |    |  |  |  |

|    | 4.3                              |                                                |                                                     |    |  |  |  |

|    | 4 4                              |                                                |                                                     |    |  |  |  |

CONTENTS 2

| 5             | $\mathbf{Sys}$   | tems with Limited Communication Buffers            | 74  |  |  |  |  |  |

|---------------|------------------|----------------------------------------------------|-----|--|--|--|--|--|

|               | 5.1              | Introduction                                       | 74  |  |  |  |  |  |

|               | 5.2              | Mathematical models                                | 76  |  |  |  |  |  |

|               |                  | 5.2.1 Star                                         | 76  |  |  |  |  |  |

|               |                  | 5.2.2 Ordinary tree                                | 77  |  |  |  |  |  |

|               |                  | 5.2.3 Binomial tree                                | 83  |  |  |  |  |  |

|               | 5.3              | Performance modeling                               | 86  |  |  |  |  |  |

|               |                  | 5.3.1 Star                                         | 87  |  |  |  |  |  |

|               |                  | 5.3.2 Ordinary and binomial trees                  | 93  |  |  |  |  |  |

|               | 5.4              | Discussion and conclusions                         | 100 |  |  |  |  |  |

| 6             | Mu               | lti-installment Divisible Job Processing           | 104 |  |  |  |  |  |

|               | 6.1              | Introduction to multi-installment processing       | 104 |  |  |  |  |  |

|               | 6.2              | The maximum gain from multi-installment processing | 110 |  |  |  |  |  |

|               | 6.3              | Processors without front-end                       |     |  |  |  |  |  |

|               | 6.4              | Processors with front-end                          |     |  |  |  |  |  |

|               | 6.5              | 5 Model Comparison                                 |     |  |  |  |  |  |

|               | 6.6              | Memory utilization in multi-installment processing | 125 |  |  |  |  |  |

|               | 6.7              | Conclusions                                        | 131 |  |  |  |  |  |

| 7             | Pra              | Practice of Divisible Job Processing               |     |  |  |  |  |  |

|               | 7.1              | Method of experimenting                            | 132 |  |  |  |  |  |

|               | 7.2              | Test applications                                  | 134 |  |  |  |  |  |

|               | 7.3              | The results                                        | 136 |  |  |  |  |  |

|               | 7.4              | Discussion and conclusions                         | 142 |  |  |  |  |  |

| 8             | Sun              | ummary                                             |     |  |  |  |  |  |

| $\mathbf{St}$ | reszo            | czenie w języku polskim                            | 147 |  |  |  |  |  |

| Bibliography  |                  |                                                    |     |  |  |  |  |  |

| Α             | Notation Summary |                                                    |     |  |  |  |  |  |

## Chapter 1

## Introduction

The need for computing power caused that parallel and distributed computing gains popularity over the recent years. Contemporary applications have very high computing power requirements. One of the most resource demanding applications are genotype sequencing, quantum chemistry and Earth simulation. In most of the cases a single computer is not able to provide computing power satisfactory for needs. Therefore parallel and distributed algorithms and application, which can run on hundreds of processors in the sam time, are necessary. Some parallel applications are run in dedicated supercomputing environment (e.g. NEC supercomputer house for Earth Simulation project). In other projects application are run on existing clusters of computers, or even on personal computers (PCs) made available by the volunteers in Internet.

In the seventieth and eightieth processors used in supercomputers were very expensive and powerful in comparison to the popular processors used in home and office computers. Over the years the technology of processors evolved and now most often supercomputers are build from similar processors and components as PCs. Almost all supercomputer vendors offer machines built from typical commodity-of-the-shelf components. The main difference between PCs and supercomputers now is the number of processors. The fastest supercomputers can be build of hundreds and thousands of processors. One eminent example is the ASCI initiative which resulted in creation

of supercomputers that are in the top of the TOP 500 Supercomputers list [1]. Some of them have several hundreds of processors. For example: .

Recently also grid technologies developed. The idea of the grid is to connect existing computers into some kind of distributed supercomputer. In this way it is easy to achieve very large computing power using standard equipment. In some projects computing power comes from thousands of PC made available by volunteers. Some example are SETI@home project [2], Mersenne Number Project [3], Entropia [4], Distributed Net [5], Folding@home [6] and other.

It should be obvious now that it is necessary to use parallel and distributed algorithms to speed up computations. Creating fast and effective parallel algorithms requires appropriate models of computation. In order to precisely simulate a complex parallel or distributed environment, many parameters and dependencies should be taken into account. A detailed model can be precise but useless because of its complexity. To many parameters result in clutter and obfuscation. Detailed models may complicate understanding of the fundamental phenomena taking place. Therefore, there is a need for specific models of parallel computations that can be a good compromise of detail and correctness.

In this work we consider the divisible job processing model. Divisible jobs can be divided into parts of arbitrary sizes and the parts can be independently processed in parallel. This means that the granularity of the computations is fine, and can be neglected as not restricting the load size selection. There are no order constraints and all parts can be processed in parallel.

This model applies, for example, to processing large measurement data sets (e.g. SETI@home [2]), data mining: searching databases, text, audio, and video files, also to some applications of linear algebra, number theory (e.g. Mersenne project [3], Distributed net [5]), simulation, combinatorial optimization [6, 28, 30, 37]. Divisible load theory (DLT) can be also applied in the analysis of distributed storage systems such as video on demand systems [15], storage area networks or network attached storage systems. In this case the distribution of the information can be optimally

geared to the speeds of the communication network, and transfer rate of the storage devices. The divisible job processing model is a very effective tool for analyzing different topologies of distributed environments: linear arrays, stars, rings, trees, meshes and hypercubes. Practical experiments proved that the divisible job processing model complies with the results of running jobs in real environments.

The purpose of this work is to examine the impact of different memory systems on the performance of divisible load processing in various distributed networks. Three kind of memory systems are considered: hierarchical memory, single level memory with limited buffer size, and systems with limited communication buffers.

Before going into further details let us outline the contents of the thesis. In Chapter 3 systems with single memory level are considered. Chapter 4 is devoted to the systems with hierarchical memory. In Chapter 5 systems with limited communication buffers are presented. In Chapter 6 the impact of multi-installment divisible job processing on the performance is examined. Real divisible jobs experiments are presented in Chapter 7. The main notation and symbols used in this work are summarized in Appendix A.

## Chapter 2

## Divisible Job Model Fundamentals

In this chapter we provide basic assumptions of the divisible load theory. The abstraction of computer systems is presented and the subject literature is shortly reviewed.

## 2.1 Formulation of the problem

Terms divisible job and divisible load will be used interchangeably in this work. We will use word processor to denote a single processing unit with CPU, memory, disks, and network interface. The words data and load in context of the size of the load processed by processors will be used interchangeably.

We consider a system with a set of m+1 uniform processors  $\mathcal{P} = \{P_0, \ldots, P_m\}$  with the additional coordinating processor called master or originator. It is assumed that at the beginning of the computation the whole volume of load with size V is located in the memory of the master processor  $P_0$ . Originator scatters the load to m processors of the distributed computer network. In every transmission the communication startup time elapses between the initiation of the communication and sending the first byte through the link. Transferring x units (e.g. bytes) of the load over link i lasts  $S_i + xC_i$  units of time (e.g. in seconds). Thus, the communication delay includes constant startup time  $S_i$  and linear component  $xC_i$  depending on the amount of the transferred data. Computing x units of the load takes  $xA_i$  units of time

on processor  $P_i$ . Sizes of the data pieces sent to processors are denoted by  $\alpha_0, \dots, \alpha_m$ .  $\alpha_i$  is the fraction of the volume V which is sent to processor  $P_i$ . Sum of all  $\alpha_i$  pieces is equal 1.

For a given computing environment (described by parameters  $C_i$ ,  $A_i$ ,  $S_i$ , V, m) the values of  $\alpha_0, \dots, \alpha_m$  should be such that the length of the schedule, denoted as  $C_{max}$  is the shortest possible.

In the following sections we introduce scattering algorithms dedicated to three message routing topologies: a star, an ordinary tree and a binomial tree.

## 2.2 System architecture

Here we make several assumptions on the nature of the computer system and the application.

The originator  $P_0$  can participate in computation or it can only distribute the load to other processors. It does not change significantly the model because if the originator computes, then it can be represented as an additional processor in a model with the originator communicating only. And vice versa, if we assume that the originator is computing, but in reality it is not, then its computation rate can be represented as  $A_0 = \infty$ . Thus, the originator would receive no load and  $\alpha_0 = 0$ .

It is possible to distinguish two kinds of processing elements depending on the ability to communicate and compute in parallel. The processors with communication front-end are equipped with the communication hardware, which allows for transmitting and computing in parallel. Processors without front-end can either communicate or compute.

It is accepted in the divisible load theory [19, 16, 35] that the time of returning the results of the computations to the originator can be neglected. It does not mean, however, that we exclude applications returning some results. The returning of the results can be incorporated in the divisible load model (cf. applications in [9, 28, 30, 37]). This assumption is made for the sake of simplicity of mathematical modeling

and conciseness of the presentation.

In the following sections we define various communication topologies and strategies.

## 2.2.1 Routing topologies

In this section we present three archetypal routing topologies used in the load scattering. These topologies can be embedded in various parallel computer interconnection topologies.

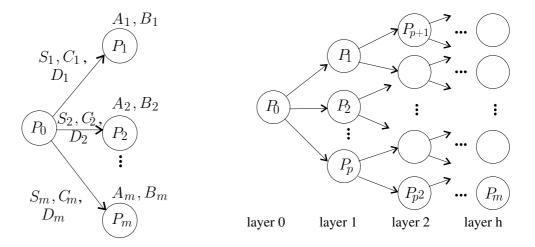

#### Star topology

In this topology the originator  $P_0$  is located in the center of the structure (cf. Fig. 2.1). All the messages are routed from the originator to the processors, or from the processors to the originator. Only one message can be sent or received by the originator at a time. This kind of communications is typical of the bus and can be considered as equivalent to the star interconnection. Hence, the star topology can represent a network of workstations, master-slave, or client-server computations [37]. This interconnection applies also to the networks in which the originator is able to address each slave processor directly, and send load to it. If it is the case then the intermediate communication nodes (if any) can be represented only as an additional communication delay. Therefore, star topology can be called direct communication topology, as well. This is especially justified in communication networks with wormhole routing or circuit switching, for which communication delay does not depend significantly on the distance between the sender and the receiver.

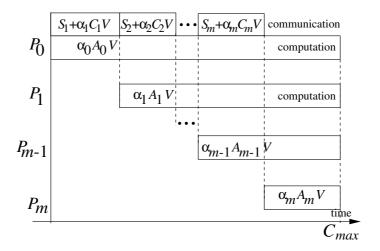

In the star network originator sends chunk  $\alpha_i V$  of load to processor  $P_i$ . Immediately after receiving its load  $P_i$  starts computing, while the originator immediately starts the communication with the next processor.

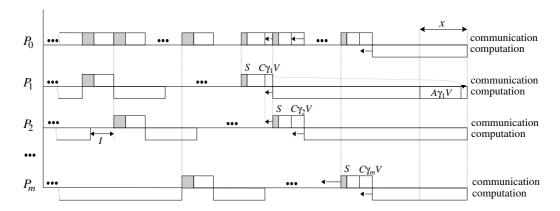

The process of communication and computation is presented in Fig. 2.3. Processing rate of processor  $P_i$  is denoted  $A_i$ . Communication links are characterized by startup time  $S_i$  and communication rate  $C_i$ . If the memory buffer of the processors

is limited then its size will be denoted  $B_i$  for buffer of processor  $P_i$ , and  $D_i$  for the communication buffer of link i.

Star topology is also called a single level tree network in the divisible load literature.

### Ordinary tree

Ordinary tree (see Fig. 2.2) is a graph-theoretic structure used in many broadcasting and scattering algorithms for various interconnection topologies [51]. The originator is not able to communicate with all processors directly. Therefore, intermediate processors are used to relay the load to other processors. We consider regular balanced tree in which nodes have out-degree p. p is also the number of ports in each processor that can be used simultaneously to activate other processors. If a processor receives some load to relay, it divides it into p equal parts and retransmits them to the still inactive processors. The set of processors in equal distance from the originator (measured in the number of hops), will be called a *layer*. Let h denote the height of the tree. We assume that the communication medium, and processors are homogeneous. Processing rate is denoted A, communication parameters are denoted S, C. The sizes of memory buffers, if limited, will be denoted B. Processors in the same layer perform the same actions, communicate and compute synchronously. Hence, processors in a layer performs identically and we seek load fractions  $\alpha_0, \ldots, \alpha_h$  assigned to each of the processors in layers  $0, \ldots, h$  respectively. The ordinary tree has  $m = \frac{p^{h+1}-1}{p-1}$ processors, for p > 1.

Note that linear array of processors, a.k.a. a chain topology is just an ordinary tree topology with degree p=1

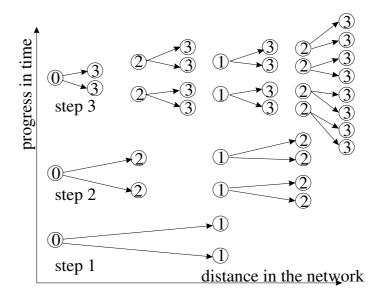

## Binomial tree

Binomial tree has been introduced in [57] as a broadcasting structure for a 2-dimensional mesh, and as a scattering structure for 1-, 2-, and 3-dimensional meshes in [27, 35, 36]. Binomial tree (cf. Fig. 2.4) is a tree in which nodes have out-degree p. Each processor

Figure 2.1: Star interconnection.

Figure 2.2: Tree interconnection.

Figure 2.3: Communication and computations in star interconnection.

Figure 2.4: Binomial tree. Numbers indicate layers.

(node) in level  $0, \ldots, i-1$  activates p new processors on level i, for  $i=1,\ldots,h$ . The set of processors in the same level of the binomial tree will be called a *layer*. Binomial tree takes advantage of the communication delay structure typical of circuit switching and wormhole routing. For these two commutation methods communication delay does not depend significantly on the distance covered by the message. Therefore, it is advantageous to send the load to processors in physically large distance from the originator first, and then to redistribute the load locally in a smaller sub-network. Note that a processor in layer i receives load to be redistributed among its descendants in layers  $i+1,\ldots,h$ .

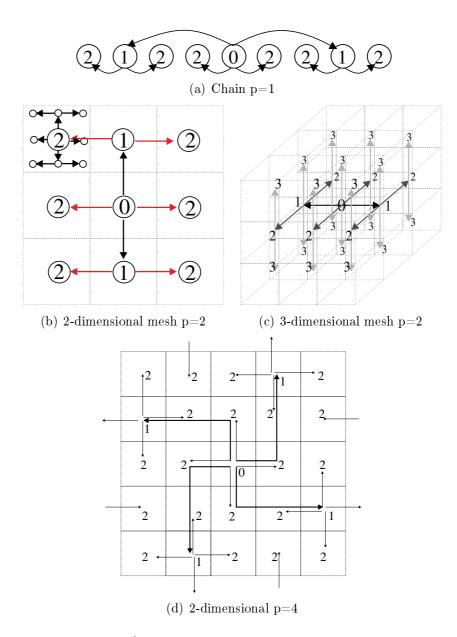

Chain, mesh, torus, hypercube or multistage interconnection can be modeled using binary tree topology. Examples of embedding binomial trees in different interconnections are shown in Fig. 2.5.

We assume that the communication medium, and processors are homogeneous. Therefore, processors in the same layer work synchronously, i.e. perform the same actions simultaneously. As in the ordinary tree we assume that processors are able to divide the received message into equal parts and simultaneously redistribute the parts to its p ports. The number of processors in a binomial tree with layers  $0, \ldots, h$

Figure 2.5: Examples of embedding binomial trees into different topologies.

is  $m = (p+1)^h$ . There are  $p(p+1)^{i-1}$  processors in layer  $1 \le i \le h$ . Our goal is to find distribution of the load  $\alpha_0, \ldots, \alpha_h$  among the processors in layers 0 to h respectively, such that schedule length  $C_{max}$  is minimal.

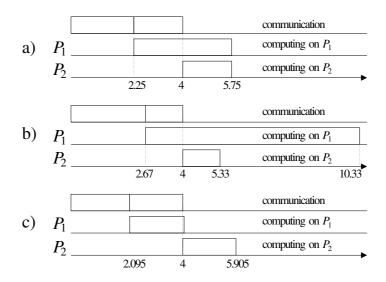

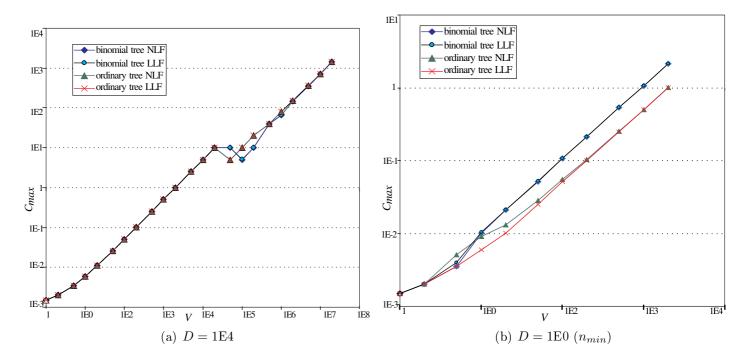

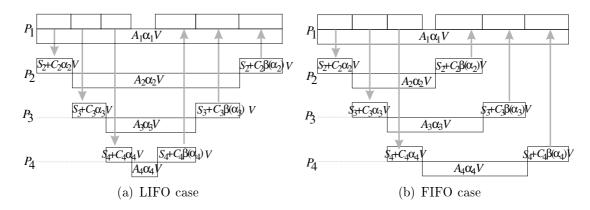

## 2.2.2 Layer activation order

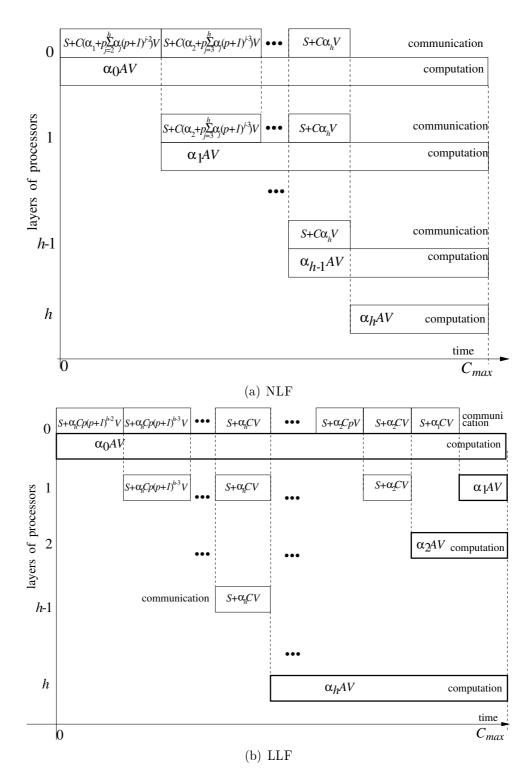

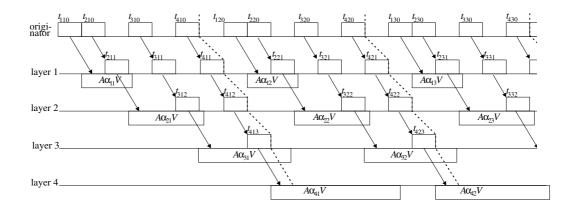

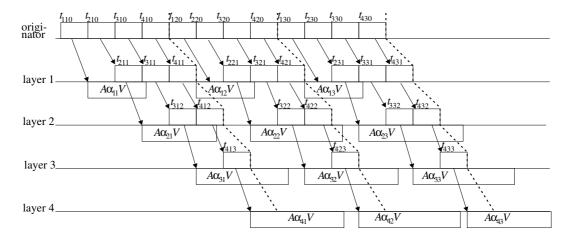

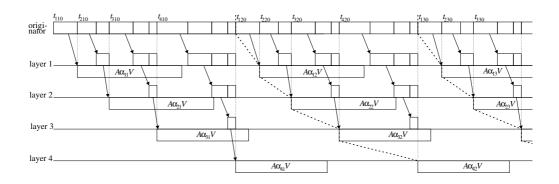

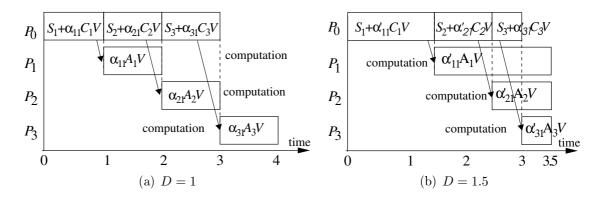

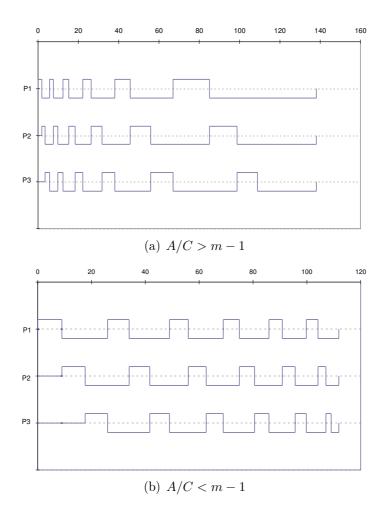

For binomial trees two different ways of activating the layers have been proposed: The natural order of the layers called NEAREST LAYER FIRST (NLF) [27], and the order of decreasing number of processors in the layer called LARGEST LAYER FIRST (LLF) [45]. Fig. 2.6 shows diagrams of communication and computation for strategies NLF, LLF, respectively. In NLF (cf.Fig. 2.6(a)) layers are activated in the order of the growing distance from the originator layer and receive the load for themselves and for their descendants. Immediately after receiving the load processors start processing their share of the load, while the rest is sent to the following layers. Thus, processors start computing in the order of the layer number. In LLF strategy (cf. Fig. 2.6(b)) the layers start computing in the order  $h, h-1, \ldots, 1$ . To activate some layer i the intermediate layers  $0, \ldots, i-1$  transfer the load to layer i, but do not compute. It was demonstrated in [45] that LLF is optimal activation sequence for binomial trees when there are no memory limitations in the computer system. It has also been demonstrated in [38] that it is not optimal when processors have limited memory buffers. We consider it also in Section 3.2.2. Both layer activation orders can be applied to the ordinary tree topology, too. We write about it in more detail in Section 5.2.2. Observe that the layer activation order does not apply to the star interconnection because all processors are directly accessible from the originator.

The actual communication interconnections will be modeled using the three topologies described above.

## 2.2.3 Single-installment and Multi-installment processing

In most of the works regarding divisible jobs, single-installment processing has been assumed. This means that every processor receives its portion of the load only once.

Figure 2.6: Layer activation order in binomial tree.

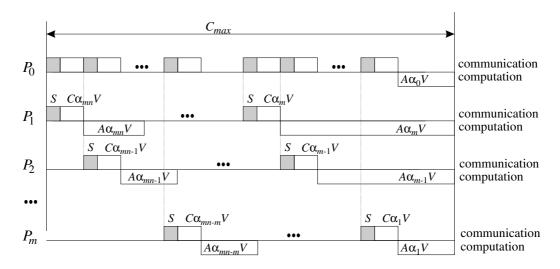

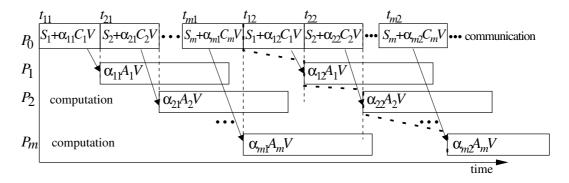

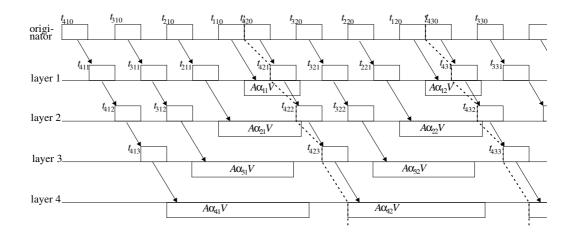

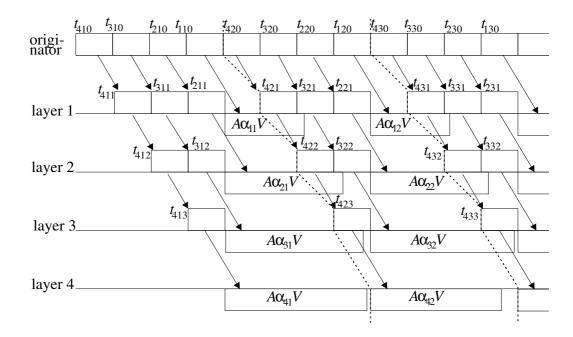

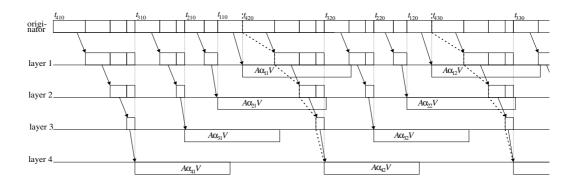

Figure 2.7: Gantt chart for multi-installment processing.

If processors receive data more than once, the processing is called multi-installment. We consider the regular type of multi-installment divisible job processing in this work. In this model data are sent to the processor many times and the processors are repeatedly activated in the same order. The load is sent in n cycles, so that after sending a piece to the last processor  $P_m$  the next piece is sent to the first processor  $P_1$ . As a result every processor gets an equal number of data pieces to process. In a system without communication front-end the originator  $P_0$  starts computing its share of the load after the communications with all processors  $P_1, \dots, P_m$ . An example Gantt chart for regular multi-installment processing in heterogeneous system is shown in Fig. 2.7.

In general processors can be activated different number of times and in any order. This kind of irregular activation is not the subject of this work.

Also in multi-installment processing we assume a nonzero startup time. With the zero startup time it is possible to prove that communications should be done in the infinite number of steps, and therefore, it is unrealistic.

## 2.3 Survey of the Earlier Results

In this section we give a short survey of the divisible load theory (DLT) literature.

Initially the divisible load processing model was used to analyze the trade-off between computation and communication in a distributed network of intelligent sensors. Divisible load model has been introduced in [32], where a linear array of intelligent sensors was considered. The problem was to find optimum balance between advantages of distributed computations on the measurement data, and the costs of communication. The same problem for bus network of sensor driven processors was considered in [11]. Later on, divisible load model has been generalized and extended in various directions.

Divisible jobs scheduling can be applied to many interconnection topologies. It was thoroughly studied for linear arrays [42, 44], busses [10, 12, 62, 64], trees [9, 10, 17, 33, 31, 50], 2D-meshes [24], 2D-toroidal meshes [27], 3D-meshes [36, 46], hypercubes [23, 47] and partitionable networks [52].

The model of communication delay has been generalized by the inclusion of the communication startup costs in [25]. The influence of startup costs on the time performance was also analyzed in [21]. The problem of scheduling divisible load with taking into account the processor release times at the time of load origination was considered in [20, 35]. Both the load distribution and results collection overheads were taken into account in [9, 25, 37].

Divisible load model was capable of incorporating sophisticated communication methods: distributing data in multiple installments [18, 19, 38, 69]. In [18] closed-form solutions were derived for homogeneous single-level tree networks. Subsequently the multi-installment strategy was applied to linear networks and closed-form solutions for processing time for homogeneous networks was presented in [19]. In [69] multi-installment processing with startup costs has been studied and maximum possible gain of regular multi-installment processing for bus networks has been derived. Multi-installment processing as a result of limited memory buffers is considered in [38]. The most of the studies consider the situation that only one load (i.e. one job)

is available for processing. This assumption was relaxed in [63] and a scheduling algorithm employing single installment strategy with FIFO order of the tasks was presented.

Memory limitations at the processor side have been considered in [22, 38, 53]. In [53], the issue of finite size buffers at the processors is addressed for the case of single level tree networks. An off-line algorithm, referred to as Incremental Balancing Strategy(IBS) was proposed. It generates load fractions in an incremental fashion. In each increment distribution of the load is found for processors with available memory according to the standard divisible load theory methods [19], without taking the memory constraints into account. Then, the distribution of the load is scaled proportionately such that at least one buffer is filled completely. The remaining available buffer capacities are the memory sizes in the next increment. It has been also demonstrated that the rule for optimum processor activation sequence proposed in [19] does not work in the case with limited memory. IBS algorithm is not optimal, which will be shown in Chapter 3 using linear programming approach. In [22], approximation algorithms were proposed to generate and round the load fractions for single installment as well as for a strategy in which the load is constrained to have at most K partitions. Ultimate performance bounds were derived for these strategies with integer approximation.

Despite its ability of analyzing intricate details of distributed computer systems, divisible load model remained computationally tractable. In many cases it was even possible to find analytical solutions of the considered models. In [32] a heterogeneous linear network of processors was considered. Under the assumption that all processors stop computation at the same time an algorithm was developed to find the optimal load fractions. The proof that this assumption is a necessary and sufficient condition for obtaining optimal processing time in linear networks appeared in [60]. An analytic proof of this assumption in bus networks without the startup times is presented in [62, 64]. In the case of single-level tree networks, a closed-form expression for the processing time and an algorithm to obtain an optimal tree configuration appeared

in [17, 50]. The optimal sequencing and optimal network arrangement were considered in [17, 23]. For homogeneous linear networks, a closed-form expression for the processing time was presented in [43] and for tree, bus, and linear networks asymptotic solutions have been derived [13, 43]. A study on arbitrary tree networks [9] presents an analytical treatment in deriving optimal sequences using the concepts of equivalent processors. The existence of the closed form analytical solutions is an advantage of the divisible load model over other deterministic scheduling models which are computationally intractable [40].

System parameters used by divisible load theory can be easily obtained in practice. Not only, was the divisible load model successful in theoretically analyzing distributed computer systems, but also its predictions have been confirmed in real computer systems [28, 30, 37, 41]. We write about it in Chapter 7. Furthermore, divisible load model was a base for analyzing multimedia retrieval systems [15], image processing [9], and cost optimization in the design of distributed systems [65]. In [41] a load distribution strategy is designed and analyzed to carry out matrix-vector product computations on a cluster of workstations. Also, this study shows the applicability of divisible load theory to design strategies that are suitable for a network of workstations. The objective of minimizing the monetary costs involved in the process of divisible load processing was analyzed in [65, 61]. The study of monetary costs minimization using DLT resulted in US patent no. 5889989 for a load sharing controller for optimizing monetary costs [61].

It can be concluded that divisible load theory is a new versatile paradigm of distributed computing. Surveys on divisible load processing can be found in [16, 19, 26, 35]. A short summary of the divisible job approach from the more than ten years perspective can be found in [59].

## Chapter 3

## Systems with Single Memory Level

In this chapter we analyze computer systems with limited memory sizes. Each processor can hold only an amount of load limited by the size of available memory. In clusters of workstations it appeared [37] that the linear dependence of processing time on the size of work is satisfied only if the computations are restricted to the core memory (RAM). Larger work chunks imply using virtual memory. When virtual memory is used, the dependence of processing time on the amount of data becomes more complex. Also the processing speed of the computers is lower. Hence, for efficiency reasons it is preferable to avoid using virtual memory and restrict the load to limited amount  $B_i$  of core memory available at processor  $P_i$ . Values of  $B_i$  are determined by the computing environment and are constant. To focus on direct impact of the buffer sizes relative to the volume V we introduce also variables  $B'_i$  which denote buffer sizes relative to the value of V, i.e.  $B'_i = \frac{B_i}{V}$ .

We assume that the critical restriction on the size of memory is put during the computation phase. It can be the case of problems where small data sets are unpacked or big data structures arise in computation from small amount of the input data. Therefore, the size of communicated message is not limited otherwise than by the memory capacity of the receiver.

In the following sections we study the computational complexity of the problem. Than we analyze the problem of optimum load distribution under the assumptions of a fixed and arbitrarily chosen processor activation sequence.

## 3.1 Complexity of divisible job scheduling with limited memory buffers

In this section we will prove that scheduling divisible load in systems with limited memory is NP-hard.

**Theorem 3.1.** Scheduling a divisible job in a star network with limited memory buffers is NP-hard.

**Proof.** We show that our problem is **NP**-hard by Turing reduction of the PAR-TITION problem:

#### **PARTITION**

Given set  $E = \{a_1, \ldots, a_q\}$  of integers decide if there exists set  $E' \subset E$ , such that  $\sum_{j \in E'} a_j = \sum_{j \in E - E'} a_j = \frac{1}{2} \sum_{j=1}^q a_j = L$ . Without loss of generality we assume that all  $a_i$  are even (which can be achieved e.g. by multiplying all  $a_i$ 's by 2).

The reduction consists in the construction of the divisible job instance on the basis of the PARTITION instance. The first instance can be answered positively if and only if for the second one the answer is positive. Construction of the scheduling instance is as follows: m = q + 1,  $V = L^6 + L$ ,  $C_1 \dots C_m = 0$ ,  $S_i = a_i$ ,  $A_i = \frac{L}{a_i}$ ,  $B_i = a_i$  for  $i = 1, \dots, q$ ,  $S_m = L$ ,  $C_m = 0$ ,  $A_m = \frac{1}{L^6}$ ,  $B_m = L^6$ . The originator  $P_0$  does not compute, i.e.  $A_0 = \infty$ . We ask if it is possible to process volume V of load on the above network in time at most 2L + 1.

Suppose the answer to the PARTITION is positive and E' is a set for which  $\sum_{j\in E'} a_j = L$ . Now, we are able to construct a feasible schedule for the scheduling problem: First, the processors with indices corresponding to the elements of E' are sent load  $\alpha_i V = a_i$ , for  $i \in E'$ , in time L. This part of the work is completed not later than at 2L. Then,  $P_m$  receives load  $L^6$ , and completes at 2L + 1 (cf. Fig. 3.1).

Now suppose the answer to the scheduling problem is positive. This means that

Figure 3.1: Illustration to the proof of Theorem 3.1.

$L^6 + L$  units of load can be processed in 2L + 1 units of time. Consequently  $P_m$  must be used because only  $P_m$  has sufficient memory size. Communication with  $P_m$  takes L units of time and L+1 units of time remain available for communication with other processors in some set F. Since all  $S_i$  are even (because  $a_i$  are even) only L units of time can be used for communications. Communications to processors in F last  $\sum_{i \in F} S_i = \sum_{i \in F} a_i \le L$ . On the other hand the processors in set F must compute at least  $V - \alpha_m V \ge L$  units of work. Hence, we have  $\sum_{i \in F} a_i = \sum_{i \in F} a_i \ge \sum_{i \in F} \alpha_i \ge L$ . Together we have  $\sum_{i \in F} a_i = L$ , and the answer in PARTITION is also positive.  $\square$

## 3.2 Fixed processor activation sequence in systems with limited memory

In this section we propose a new method of finding solutions with guaranteed optimality for the problem of scheduling divisible loads in networks of processors with limited memory and communication startup times. The method introduces mathematical programming to the realm of divisible load theory. We analyze two network types: star and binomial tree. The implications of memory limitations for the performance are studied.

## 3.2.1 Star

We assume that the originator both communicates and computes, and that simultaneous computation and communication is possible. We assume that the sequence of sending the load to the processors is  $P_1, \ldots, P_m$ , and is fixed. Our problem can be formulated as a linear program LP SSML (for LP Star Single Memory Level):

#### LP SSML

minimize  $C_{max}$

subject to:

$$\alpha_i V A_i + \sum_{j=1}^i (S_j + \alpha_j V C_j) \le C_{max}$$

for  $i = 0, \dots, m$  (3.1)

$$\alpha_i V \le B_i \qquad \text{for } i = 0, \dots, m$$

(3.2)

$$\sum_{i=0}^{m} \alpha_i = 1 \tag{3.3}$$

$$\alpha_i \ge 0$$

for  $i = 0, \dots, m$  (3.4)

Let us explain the above formulae. We are to minimize schedule length  $C_{max}$  by finding values of variables  $\alpha_i$ ,  $C_{max}$  such that: by equations (3.1) each processor completes not later than at  $C_{max}$ , by equations (3.2) no processor is assigned more load than the size of its memory, according to equation (3.3) all the load fractions add up to the total load. In the equation (3.1) for i = 0 we have  $\sum_{j=1}^{0} (S_j + \alpha_j V C_j) = 0$ , because no communication is needed.

LP SSML has m+2 variables and 3m+4 constraints. The solution of LP SSML is a point in m+2-dimensional space. Constraints (3.1), ..., (3.4) restrict the area of admissible solutions to a convex polyhedron. It is known that the optimum solution is located in one of the polyhedron corners. Unfortunately, the location of the optimum depends on the problem instance and no closed-form expression of  $\alpha_i$  seems possible. The linear programs can be solved in polynomial time, e.g. in  $O(m^{3.5}L)$  time [48, 54] using the interior point methods, where L is the length of the string encoding all the parameters  $(A_i, C_i, S_i, B_i, V)$  of LP SSML. Linear programs can be solved by many

public domain and licensed codes. All linear programming formulations in this work were solved by lp\_solve ver. 2.0 [14], a public domain linear programming code. Our method is more time-consuming but it is also more robust than the IBS heuristic proposed in [53]. Consider Example 3 from [53].

**Example.** m=4 (i.e. we have originator and 4 additional processors). Processing rates are:  $A_0=1, A_1=5, A_2=4, A_3=3, A_4=2$ . Available memory sizes are:  $B_0=10, B_1=20, B_2=45, B_3=15, B_4=30$ . Communication rates are  $C_1=4, C_2=3, C_3=2, C_4=1$ . All startup times are  $S_i=0$ , for  $i=1,\ldots,4$ . V=100. By solving SSML LP we obtain:

| processor | $B_i$ | $\alpha_i V$ | communication completion | computation completion |

|-----------|-------|--------------|--------------------------|------------------------|

| $P_0$     | 10    | 10           | 0                        | 10                     |

| $P_1$     | 20    | 15           | 60                       | 135                    |

| $P_2$     | 45    | 30           | 150                      | 270                    |

| $P_3$     | 15    | 15           | 180                      | 225                    |

| $P_4$     | 30    | 30           | 210                      | 270                    |

This schedule has  $C_{max} = 270$ , and is shorter than the one found by IBS algorithm in [53] by 5 units of time. This is so because the optimality of LP SSML formulation is guaranteed, whereas IBS is a fast heuristic. The length of the schedule is determined by the completion of computations on processors  $P_2$  and  $P_4$ .  $P_1$ ,  $P_2$  memories are not fully utilized. Note that in the interval [10,210]  $P_0$  is not computing but only communicating.  $\square$

#### Performance modeling

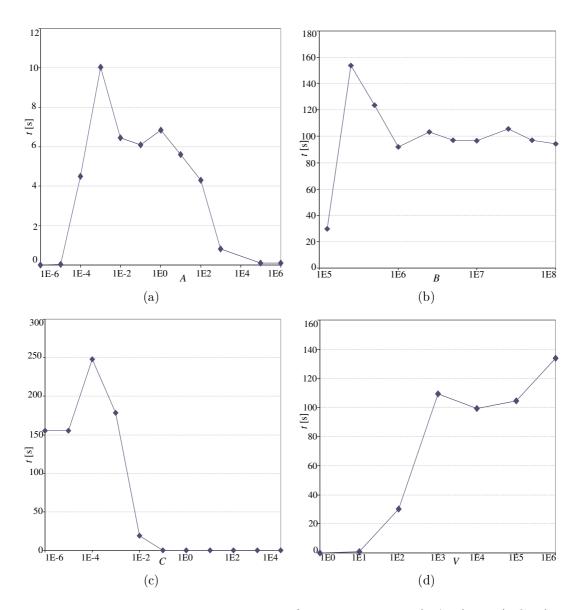

Now, we will discuss the influence of memory size on the performance of star networks.

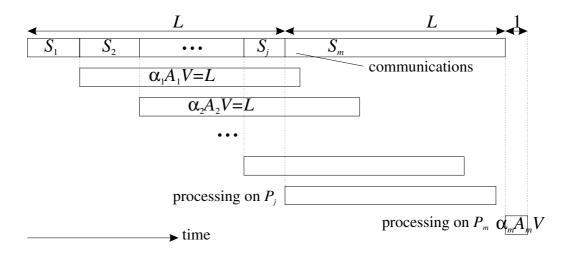

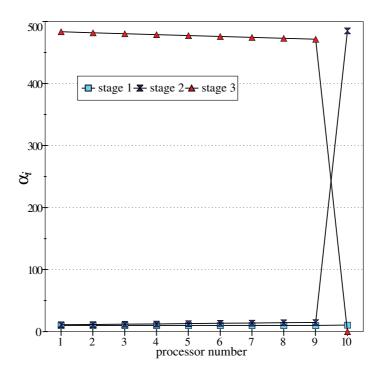

We modeled a system of initiator and 9 identical processors with  $A_i = A=1$ E-6, connected by identical communication links with startup  $S_i = S = 0.001$ ,  $C_i = C=1$ E-6. The sizes of available memory were equal B on all processors and the originator. A feasible solution of LP may not exist when the sum of buffer capacities is smaller than V. When a feasible solution existed we recorded the best solution for

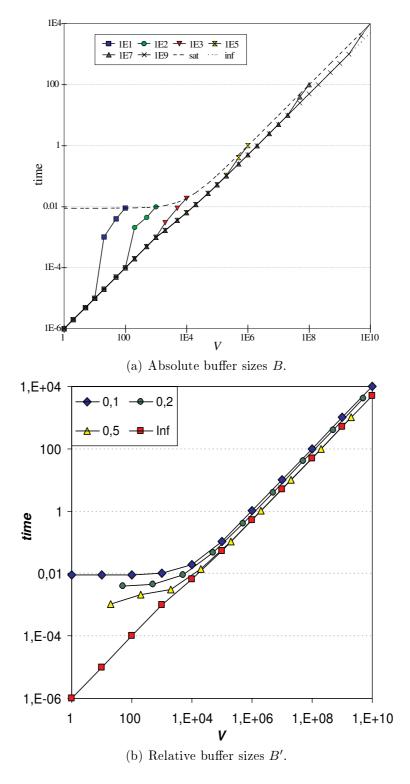

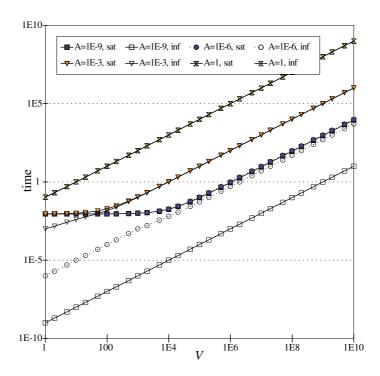

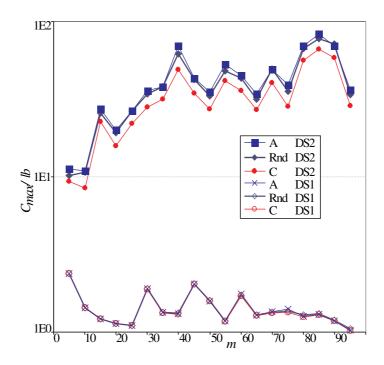

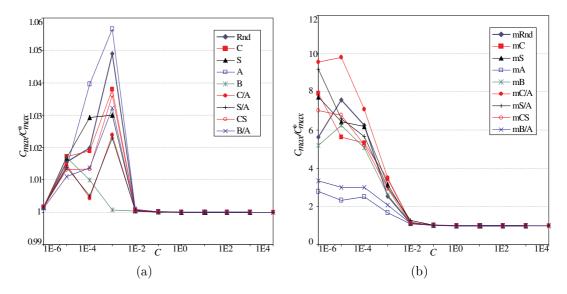

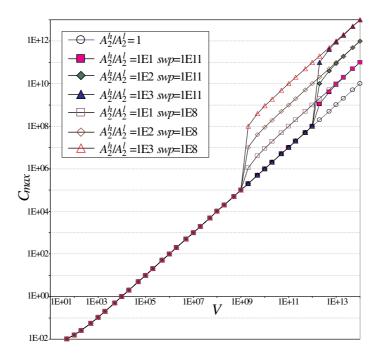

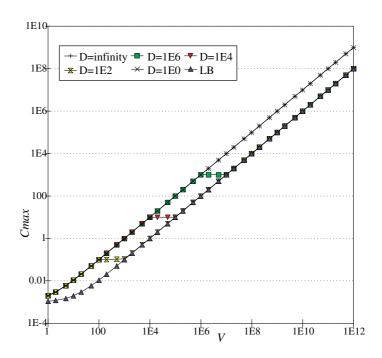

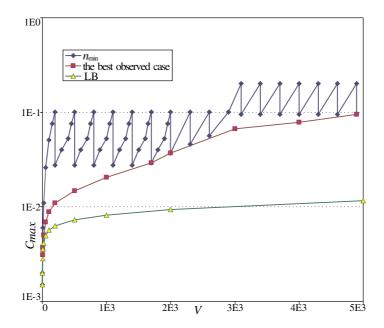

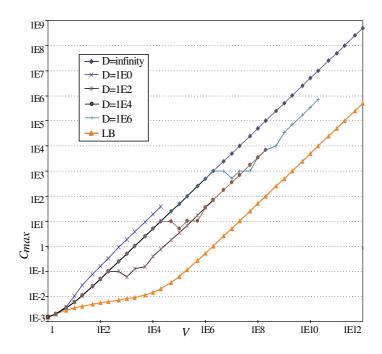

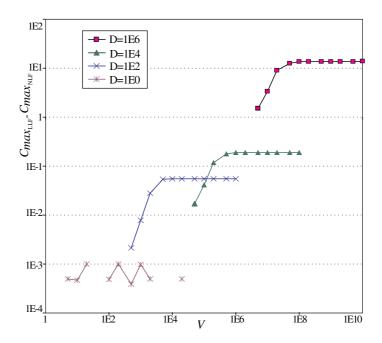

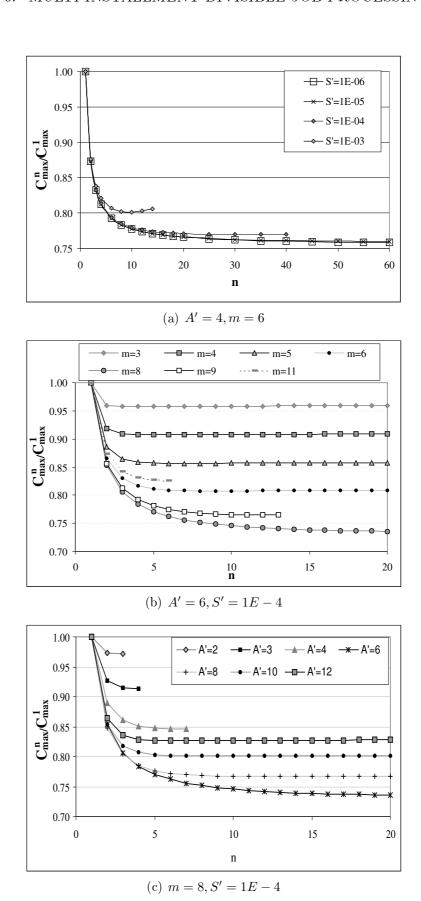

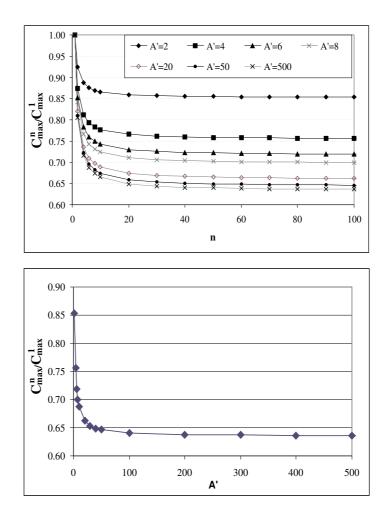

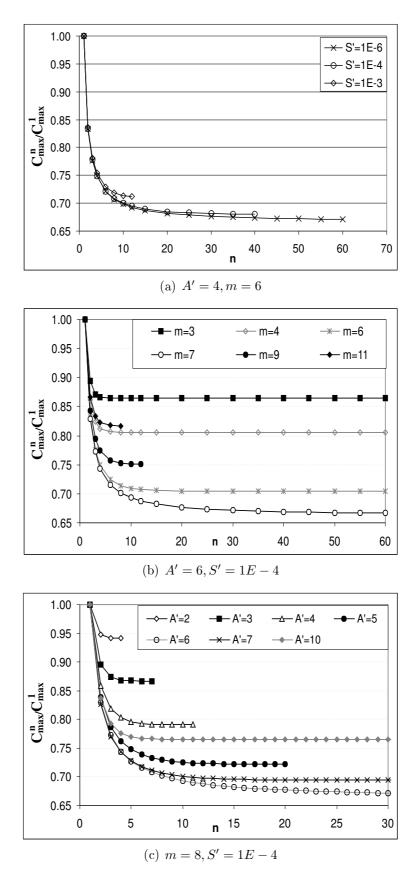

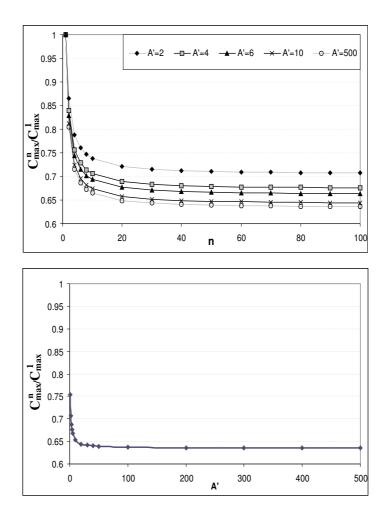

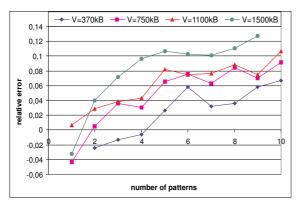

one of the number of processors from the range 1,..., 10 (including the originator). The results of modeling are collected in Fig. 3.2. On the horizontal axis we have size of the problem V, on the vertical axis we have schedule length  $C_{max}$ . Plots for memory sizes from B = 10 to B = 1E9 are presented. Fig. 3.2(a) presents schedule length for buffers sizes expressed in the absolute terms (eg. in bytes). As it can be verified with B=10 we can solve problems with size up to V=100 on ten processors. Two more reference lines denoted "sat" and "inf" are depicted in Fig. 3.2(a). Line "sat" represents a system with total memory sizes exactly equal to V. This means that  $B = \frac{V}{m+1}$  and memory buffers are saturated. Schedule length in a saturated system is  $C_{max}^{sat} = \sum_{j=1}^{m} (S + \frac{V}{m+1}C) + \frac{V}{m+1}A$ . Line "inf" represents schedule length  $C_{max}^{inf}$  in a system with unlimited memory. In this case memory size is big enough to hold any loads and we can calculate the distribution of the load according to the classical divisible load theory methods [19, 35]. The plots of processing times for particular memory sizes are located between lines "inf" and "sat". As it can be seen line "sat" approaches line "inf" at  $V \approx 1$ E4. For bigger volumes the two lines form a kind of tunnel in which schedule length for the particular memory size must fit. The width of this tunnel shows influence of memory limitation on the schedule length because its upper line represents the system which has just as much memory as needed to hold the load, while the lower line represents a system which has unlimited available memory. Fig. 3.2(b)presents schedule length for buffers sizes expressed in relative terms as the ration of V. By thre small relative difference between lines "inf" and "sat" we can conclude that for large problem sizes V the impact on memory sizes is limited. The position of processing time within the tunnel described above depends on the problem size but only on the buffer sizes relative to the problem size. From the results presented in Fig. 3.2 it can be concluded that for small problems (when V is less than 1E4), memory limitations are very important, because load imbalance may be incurred by insufficient memory sizes.

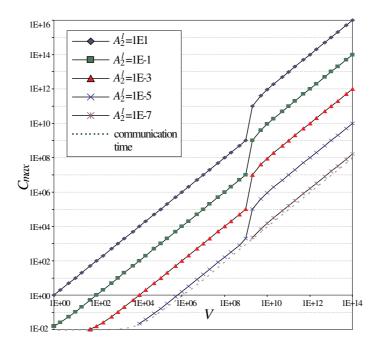

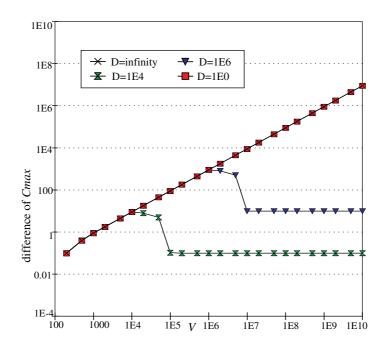

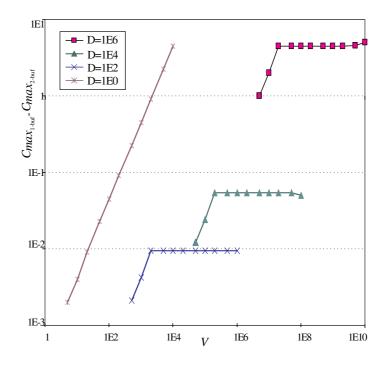

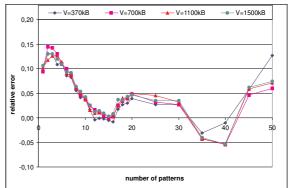

In order to demonstrate the influence of memory size constraints on  $C_{max}$  we collected in Fig. 3.3 values for the "inf" and "sat" cases for various processing rates

Figure 3.2: Schedule length for a star network depending on problem size and memory buffer size.

Figure 3.3: Schedule length for a star network with unlimited and saturated memory

A. A system with A=1E-9 has the fastest, while the system with A=1 has the slowest processors. The plots for A=1 are so close that they are drawn one on another. Also the lines for the saturated systems with A=1E-9 and A=1E-6 are so close that they are indistinguishable. For small A schedule length in saturated system is dominated by communications which last  $\sum_{j=1}^{m} (S + \frac{VC}{m+1})$ . Therefore, the lines for A=1E-9 and A=1E-6 in saturated system are very close. The increase of A results in lines "inf" going up in the Fig. 3.3. The "sat" lines must be located above "inf" lines. As A increases the difference between "inf" and "sat" decreases such that eventually for A=1 they are indistinguishable. It can be observed that for computationally intensive applications which have big A, and big volumes V the difference between "sat" and "inf" cases is small and schedule length is dominated by communication and processing speeds.

Now we will calculate width of the tunnel, i.e. the ratio of schedule lengths in the saturated and unlimited memory cases, on a set of identical processors for big problem

sizes V and computationally intensive applications. An application is computationally intensive if the total computation time AV dominates the communication time CV. In the following we denote by  $\rho = \frac{C}{A}$ , and  $\sigma = \frac{S}{A}$ .

**Lemma 3.2.** In the star interconnection  $\lim_{V\to\infty,\rho\to 0} \frac{C_{max}^{inf}}{C_{max}^{sat}} = 1$ .

**Proof.** In the saturated case  $C_{max}^{sat} = \sum_{i=1}^{m} (S + \frac{VC}{m+1}) + \frac{AV}{m+1} = mS + \frac{V(mC+A)}{m+1}$ . It was proved [19] that when results are not returned, and memory is unlimited, all processors must stop computing in the same moment of time. From this observation we infer that time  $A_i\alpha_iV$  of computing on processor  $P_i$  activated earlier is equal to time  $S_{i+1} + \alpha_{i+1}V(A_{i+1} + C_{i+1})$  of sending the load to processor  $P_{i+1}$  activated later and computing on  $P_{i+1}$ . As we consider identical processors we have:  $A\alpha_iV = S + \alpha_{i+1}V(A+C)$ .  $\alpha_iV$  can be expressed as a linear function of  $\alpha_mV$ :  $\alpha_{m-i}V = \alpha_mV(1+\rho)^i + \frac{\sigma}{\rho}((1+\rho)^i-1)$  for  $i=1,\ldots,m$ . All  $\alpha_i$ s must add up to 1. Therefore,  $V = \sum_{i=0}^m \alpha_iV = \alpha_mV\frac{(1+\rho)^{m+1}-1}{\rho} + \frac{\sigma}{\rho^2}((1+\rho)^{m+1}-1-\rho-m\rho)$ . From which  $\alpha_mV$ , and  $C_{max}^{inf} = A\alpha_0V$  can be calculated:

$$C_{max}^{inf} = \frac{A[V - \frac{\sigma}{\rho^2}((1+\rho)^{m+1} - 1 - \rho - m\rho)]\rho(1+\rho)^m}{(1+\rho)^{m+1} - 1} + \frac{A\sigma}{\rho}((1+\rho)^m - 1) \quad (3.5)$$

Finally, we have the desired ratio for big V:

$$\lim_{V \to \infty} \frac{C_{max}^{inf}}{C_{max}^{sat}} = \frac{(m+1)\rho(\rho+1)^m}{(m\rho+1)((\rho+1)^{m+1}-1)}.$$

(3.6)

For computation intensive applications  $A \gg C$  and  $\rho \to 0$ . After applying de l'Hôpital rule we obtain:

$$\lim_{V \to \infty, \rho \to 0} \frac{C_{max}^{inf}}{C_{max}^{sat}} = \lim_{\rho \to 0} \frac{(m+1)\rho(\rho+1)^m}{(m\rho+1)((\rho+1)^{m+1}-1)}$$

$$\stackrel{H}{=} \lim_{\rho \to 0} \frac{(m+1)[(\rho+1)^m + m\rho(\rho+1)^{m-1}]}{m((\rho+1)^{m+1}-1) + (m\rho+1)(m+1)(\rho+1)^m} = 1$$

(3.7)

We conclude that in the case of big problem sizes V and computationally intensive applications executed on a set of identical processors, memory limitations are not as

restrictive, for the schedule length, as computation and communication speeds. This observation is confirmed by Fig. 3.2, and Fig. 3.3. On the other hand it should not be forgotten that this result applies to homogeneous computing systems. In heterogeneous systems, the difference between  $C_{max}^{inf}$  and  $C_{max}^{sat}$  can be arbitrarily big. For example, when a fast processor has small memory buffer and a slow processor has a large buffer then the equivalent speed of the system is dominated by the slow processor in the "sat" case. Furthermore, in practice parameters A, C, S may depend on change with the amount of the assigned load [37]. We discuss it in Chapter 4 and Chapter 7.

From equation (3.6) a width of the tunnel for fixed  $\rho$ , and m tending to infinity can be derived:

#### Lemma 3.3. In the star interconnection

$$\lim_{V \to \infty, m \to \infty} \frac{C_{max}^{inf}}{C_{max}^{sat}} = \frac{e^{\frac{1}{k}}}{(e^{\frac{1}{k}} - 1)(k+1)}.$$

where  $k = \frac{A}{C(m+1)}$ .

**Proof.** Let us assume that  $\frac{C}{A} = \rho = \frac{1}{k(m+1)}$ . Then from (3.6) we have

$$\lim_{V \to \infty} \frac{C_{max}^{inf}}{C_{max}^{sat}} = \frac{(m+1)\rho(\rho+1)^m}{(m\rho+1)((\rho+1)^{m+1}-1)}$$

$$= \frac{\frac{1}{k}(\frac{1}{k(m+1)}+1)^m}{(\frac{m}{k(m+1)}+1)((\frac{1}{k(m+1)}+1)^{m+1}-1)}$$

(3.8)

After observing that  $\lim_{x\to\infty} (1+\frac{1}{kx})^x = \lim_{x\to\infty} (1+\frac{1}{k(x+1)})^x = e^{\frac{1}{k}}$  we have:

$$\lim_{V \to \infty, m \to \infty} \frac{C_{max}^{inf}}{C_{max}^{sat}} = \frac{\frac{\frac{1}{k}e^{\frac{1}{k}}}{(\frac{1}{k}+1)(e^{\frac{1}{k}}-1)}}{(\frac{1}{k}+1)(e^{\frac{1}{k}}-1)} = \frac{e^{\frac{1}{k}}}{(k+1)(e^{\frac{1}{k}}-1)}$$

(3.9)

Let us note that k has a practical meaning. If k < 1 then the processing rate for all processors Am is less than transmission rate and parallel processing has no sense for such a system. Therefore, k can be treated as a global characteristic of a system.

We finish this section with an observation on the way of activating the processors in the solutions of the linear problem LP SSML. Activation of the processors is ruled by two effects: memory limitations and schedule length minimization. When memory size on one processor is small then more processors must be used, though it is not as efficient as it would be in unlimited memory case. On the other hand, when computation times are short in relation to communication times then it is advantageous to use few processors. Hence, in our performance simulations for A = 1E-6 less machines were used for some given volume V than for A = 1E-3.

## 3.2.2 Binomial trees

In this section we consider communications in binomial trees under two activation strategies: Nearest Layer First (NLF) and Largest Layer First (LLF).

### Nearest Layer First

The problem of determining optimal distribution of load V in a binomial tree of degree p under NLF strategy can be formulated as the following linear program:

#### LP NLF:

minimize  $C_{max}$

subject to:

$$\alpha_i VA + \sum_{j=1}^i (S + C\alpha_j V + CpV \sum_{k=j+1}^h (p+1)^{k-j-1} \alpha_k) \le C_{max} \quad i = 0, \dots, h \quad (3.10)$$

$$\alpha_0 + p \sum_{i=1}^{h} (1+p)^{i-1} \alpha_i = 1$$

(3.11)

$$B \ge \alpha_i V \ge 0 \qquad i = 0, \dots, h \quad (3.12)$$

In LP NLF  $\alpha_i$ , for  $(i=0,\ldots,h)$ , are variables denoting the amount of load assigned to each processor in layer i. In inequalities (3.10) term  $\sum_{j=1}^{i} (S + C\alpha_j V + CpV \sum_{k=j+1}^{h} (p+1)^{k-j-1}\alpha_k)$  is the communication time spent until activating layer

i. Note that layers  $1, \ldots, i$  receive load not only for themselves but also the load to be redistributed to layers  $i+1,\ldots,h$ . Constraints (3.10) ensure that all layers stop computing before the end of the schedule  $C_{max}$ . By equation (3.11) all the load is processed, and by (3.12) assignments of the load can be accommodated in the memory buffers of the processors. LP NLF is formulated with the assumption that all h layers are working. However, it may happen that fewer layers will process all the load. In such a case some layers are not assigned any load, but still communication startup time appears in inequalities (3.10). This case is easy to recognize: some layers receive 0 load, and decreasing h reduces  $C_{max}$ . Hence, less layers should be used. By binary search over the admissible numbers of layers the appropriate value of h can be found.

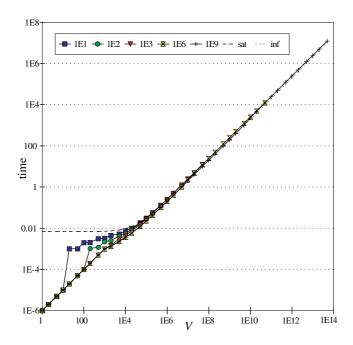

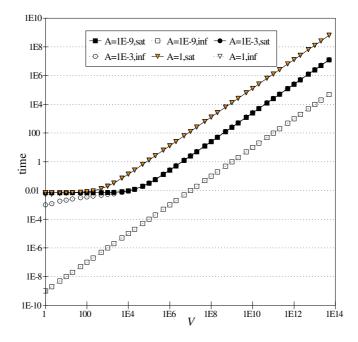

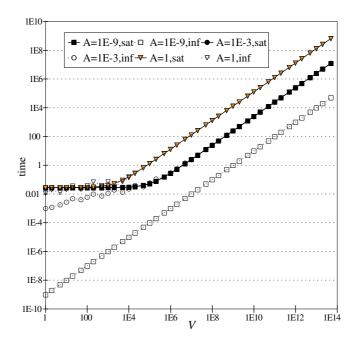

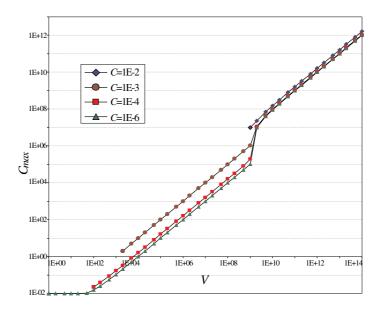

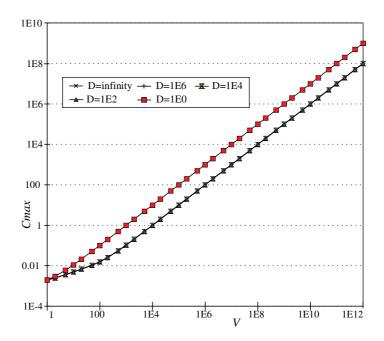

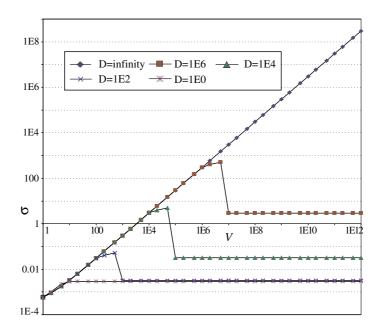

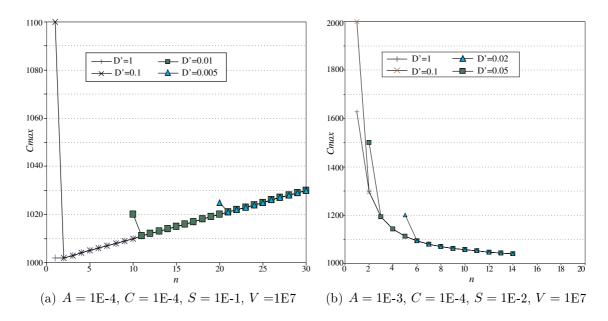

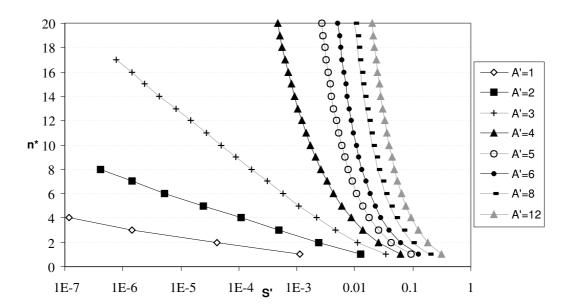

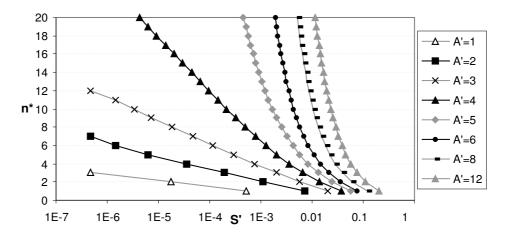

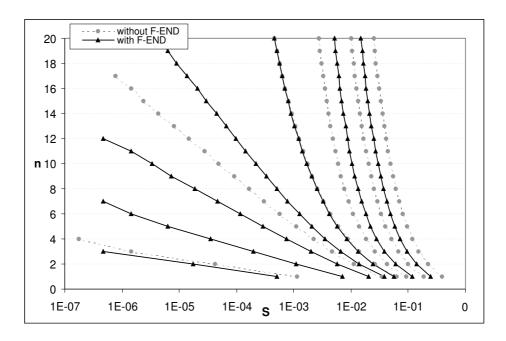

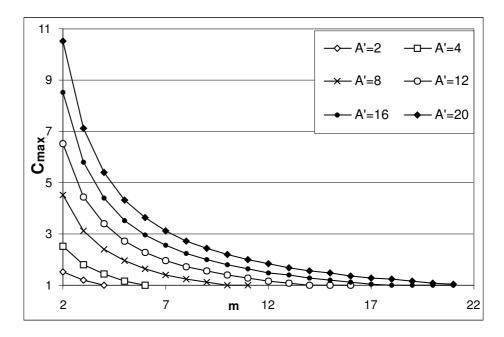

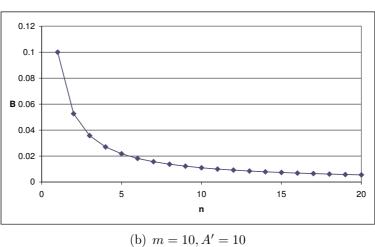

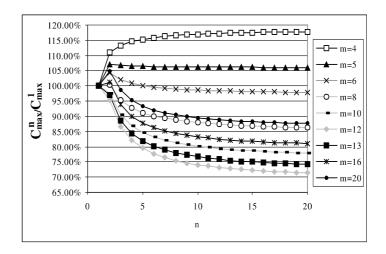

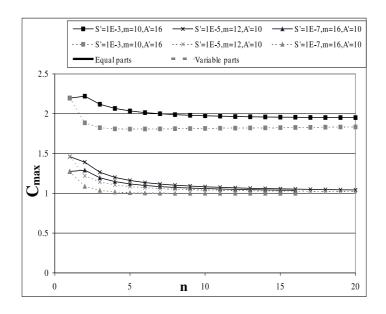

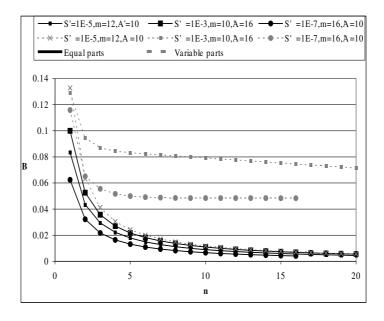

Now, we will study performance of NLF algorithm in a binomial tree of degree P=4, and with h=7 layers (m=78125 processors). This tree can be embedded into a 2-dimensional toroidal mesh as described in [27] (see Fig 2.5(d)). We modeled a system with A=C=1E-6, S=1E-3, and memory sizes from B=10 to B=1E9. The schedule lengths  $C_{max}$  vs. size of the problem is depicted in Fig. 3.4. Line "inf" represents a system with unlimited memory. Line "sat" represents a system with total memory size equal V. Thus, in saturated case each processor has memory buffer of size  $B=\frac{V}{(p+1)^h}$ . Schedule lengths for "sat" and "inf" cases are very close to each other in the case of big volumes V. As it was in the case of star topology, the two lines form a tunnel in which plots for particular memory sizes are located. In Fig. 3.5 only "sat" and "inf" cases are depicted for various processing rates A. The behavior is similar to the star topology: For big load volumes V the two lines are parallel. As A increases (e.g. because the application is computationally intensive) the "inf" line moves up until it overlaps with line "sat". Now we are going to calculate the relative width of the tunnel for big V and  $\frac{A}{C}$ .

**Lemma 3.4.** Under NLF strategy in binomial tree  $\lim_{V\to\infty,\rho\to 0} \frac{C_{max}^{inf}}{C_{max}^{sat}} = 1$ .

**Proof.** We will give a formula for the ratio of schedule length  $C_{max}^{sat}$  in the saturated case and  $C_{max}^{inf}$  in the unlimited memory case. In the saturated case all processors are assigned the same load equal to the buffers size  $B = \alpha_i V = \frac{V}{(p+1)^h}$ , for

Figure 3.4: Schedule length in a binomial tree under NLF strategy.

Figure 3.5: Schedule length in a binomial tree under NLF strategy for saturated and unlimited memory.

$i=0,\ldots,h.$   $C_{max}^{sat}$  is determined by the duration of all communications plus processing on layer h. Thus,  $C_{max}^{sat}=hS+\frac{CV}{m}\sum_{j=1}^h(1+p\sum_{k=j+1}^h(p+1)^{k-j-1})+\frac{AV}{m}$ , where  $m=(p+1)^h$  is total number of processors. This formula can be reduced to  $C_{max}^{sat}=hS+\frac{VA}{m}+\frac{VC((p+1)^h-1)}{mp}$ . The formula expressing  $C_{max}^{inf}$  has been derived in [45]:  $C_{max}^{inf}=A(V+\frac{\sigma}{p+\rho})\frac{p(p+\rho+1)^{-h}+\rho}{p+\rho}+\frac{\sigma(hp-1)}{p+\rho}$ . Hence,

$$\frac{C_{max}^{inf}}{C_{max}^{sat}} = \frac{A(V + \frac{\sigma}{p+\rho}) \frac{p(p+\rho+1)^{-h} + \rho}{p+\rho} + \frac{\sigma(hp-1)}{p+\rho}}{hS + \frac{VA}{m} + \frac{VC((p+1)^{h} - 1)}{mp}}$$

(3.13)

Since  $m = (p1)^h$  it can be verified that  $\lim_{V \to \infty, \rho \to 0} \frac{C_{max}^{inf}}{C_{max}^{sat}} = \lim_{\rho \to 0} \frac{\frac{p(p+\rho+1)^{-h}+\rho}{p+\rho}}{\frac{1}{m} + \frac{\rho((p+1)^h-1)}{mp}} = \frac{\frac{p(p+1)^{-h}}{p}}{\frac{1}{(p+1)^h}} = 1. \quad \Box$

Thus, in binomial trees spanned in homogeneous computer networks, under NLF strategy, when size V of the problem is big, and the problem is computationally intensive  $(\rho \to 0)$ , the influence of the limited memory is insignificant.

## Largest Layer First

In this section we consider a different strategy of activating the layers. According to LLF strategy h is the first layer, and 1 is the last layer activated. We will give a linear program solving the problem of distributing the load optimally in binomial tree under LLF. Then, we compare the results of modeling performance of systems with LLF and NLF scattering methods.

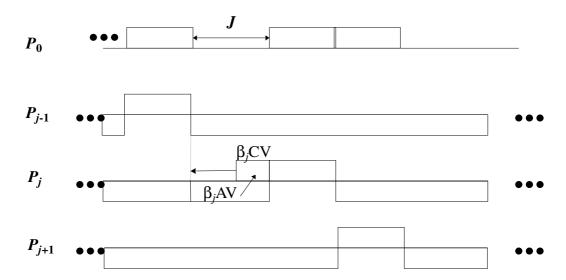

Before formulating a linear program for LLF strategy let us analyze the duration of the communication from the originator to layer i. There are  $p(p+1)^{i-1}$  processors in layer i. First, the originator sends over each of its p communication links  $p(p+1)^{i-2}\alpha_i V$  load units to layer 1. The remaining load  $p(p+1)^{i-2}\alpha_i V$  will be sent to layer i via direct successors of the originator in layers  $2, \ldots, i$  (cf. Fig. 5.6). Each processor in layer j < i-1 sends  $p(p+1)^{i-j-2}\alpha_i V$  units of data to layer j+1. The remaining  $p(p+1)^{i-j-2}\alpha_i V$  units of the load are sent from layer j to layer i via j's direct binomial tree successors in layers  $j+1, \ldots, i$ . Finally, layers  $0, \ldots, i-1$  send  $\alpha_i V$  load units to layer i. Note that all layers communicate synchronously, and the same amounts

of load are sent from active layers to the next activated layer. Total communication time is equal to  $Si + C\alpha_i V(1 + p \sum_{j=0}^{i-2} (p+1)^{i-j-2}) = Si + C\alpha_i V(p+1)^{i-1}$ . The problem can be solved by a linear program:

#### LP LLF:

minimize  $C_{max}$

subject to:

$$\alpha_i V A + \sum_{j=i}^h (Sj + C(p+1)^{j-1} \alpha_j V) \le C_{max}$$

$i = 0, \dots, h$  (3.14)

$$\alpha_0 + p \sum_{i=1}^h (1+p)^{i-1} \alpha_i = 1$$

(3.15)

$$B \ge \alpha_i V \ge 0 \qquad \qquad i = 0, \dots, h \tag{3.16}$$

In LP LLF inequalities (3.14) guarantee that all processors finish computing before the end of the schedule. By equation (3.15) all the load is processed, and by constraints (3.16) all processors are able to accommodate the assigned load. It may happen that the assumed number of layers h is too big and a reduction of h results in shorter schedule. Yet, the problem becomes more involved because we send to the larger layer first. A solution of LP LLF may activate layers non-continuously. Some layers may receive load for processing, while the remaining layers would still contribute startup time S in inequalities (3.14), though they receive nothing. We observed that in the solutions of LP LLF layers with higher index (i.e. with more processors) are assigned some load first in consecutive manner (without gaps). Thus, for the given h it is possible to check LP LLF only with the last layers  $h, \ldots, h-j$ . The best number of utilized layers can be found by binary search over the range of h. In the worst case this procedure must be repeated for various values of h. Hence, the total number of calls to LP LLF needed to find optimum distribution of the load is  $O(h \log h)$ , where  $h = \log_{p+1} m$ , and m is the number of available processors. In the following we prove that this strategy leads to optimal solutions because it is always profitable to activate layer i + 1 (with more processors) before layer i.

**Lemma 3.5.** Let  $C^i_{max}$  denote schedule length for some volume V assigned to layer i but not to layer i+1, and  $C^{i+1}_{max}$ , when V is assigned to i+1, but not to i. Then,  $C^i_{max} > C^{i+1}_{max}$ .

**Proof.** Let us calculate length of the schedule when layer i is used to process V, but layer i+1 is not exploited. Layer i has  $p(p+1)^{i-1}$  processors. Thus,  $C^i_{max} = S + C(p+1)^{i-1} \frac{V}{p(p+1)^{i-1}} + \frac{AV}{p(p+1)^{i-1}} = S + \frac{CV}{p} + \frac{AV}{p(p+1)^{i-1}}$ . Analogously,  $C^{i+1}_{max} = S + \frac{CV}{p} + \frac{AV}{p(p+1)^i}$ . Hence,  $C^i_{max} > C^{i+1}_{max}$  for i > 0.  $\square$

By the above lemma it is profitable to activate the layers consecutively from the layer with more processors to the layer with less processors (without gaps in between).

We studied the performance of a computer network with embedded binomial tree under LLF strategy. In order to find the shortest processing time over various orders of activating layers we used the result of Lemma 3.5, and increased the number of active layers from the last one to the first. The solution with the smallest schedule length was selected. In general, the behavior of  $C_{max}$  under changing V, B, A is very similar to the case of NLF behavior. Schedule lengths in the saturated system and in the system with unlimited memory is presented in Fig. 3.5. Also here a tunnel between "inf" and "sat" cases can be observed. In the following lemma we will show that for big volumes and computation-intensive applications the relative difference between the "inf" and "sat" cases is very small.

**Lemma 3.6.** Under LLF strategy in binomial tree  $\lim_{V\to\infty,\rho\to 0} \frac{C_{max}^{inf}}{C_{max}^{sat}} = 1$ .

**Proof.** Schedule length in the saturated case is  $C_{max}^{sat} = \sum_{j=1}^{h} (Sj + \frac{VC}{m}(p+1)^{j-1}) + \frac{AV}{m} = S(h+1)h/2 + \frac{V}{m}(C_{m-1}^{m-1} + A)$ , where  $m = (p+1)^h$  is the total number of processors. The formula for  $C_{max}^{inf}$  has been given in [45]:

$$C_{max}^{inf} = \frac{AV}{M} + \frac{A\sigma p}{\rho M} \sum_{j=1}^{h} \frac{c_{\pi(j)} - 1}{P_j^{\pi}} (\sum_{j=1}^{i} (h - i + 1) P_{i-1}^{\pi}),$$

where:  $M = 1 + \frac{p}{\rho} (1 - \frac{1}{P_h^{\pi}}), c_{\pi(j)} = 1 + \rho(p+1)^{h-j}, c_{\pi(0)} = 1, \text{ and } P_j^{\pi} = \prod_{i=0}^j c_{\pi(i)}.$

Figure 3.6: Schedule length in a binomial tree under LLF strategy with unlimited and saturated memory

Thus in LLF strategy,

$$\frac{C_{max}^{inf}}{C_{max}^{sat}} = \frac{\frac{AV}{M} + \frac{A\sigma p}{\rho M} \sum_{j=1}^{h} \frac{c_{\pi(j)} - 1}{P_{j}^{\pi}} (\sum_{i=1}^{j} (h - i + 1) P_{i-1}^{\pi})}{S(h+1)h/2 + \frac{V}{m} (C_{\frac{m-1}{p}}^{m-1} + A)}$$

(3.17)

When the volume of load is big and the application is computationally intensive, we have:

$$\lim_{V \to \infty, \rho \to 0} \frac{C_{max}^{inf}}{C_{max}^{sat}} = \lim_{V \to \infty, \rho \to 0} \frac{\frac{VA}{1 + \frac{p}{\rho}(1 - \frac{1}{P_h^{\pi}})}}{\frac{VA}{m}(\rho \frac{m-1}{p} + 1)} = \lim_{\rho \to 0} \frac{m}{(1 + \frac{p}{\rho}(1 - \frac{1}{P_h^{\pi}}))(\rho \frac{m-1}{p} + 1)} = \lim_{\rho \to 0} \frac{m}{1 + \frac{p}{\rho}(1 - \frac{1}{P_h^{\pi}})} \stackrel{H}{=} 1$$

since

$$\lim_{\rho \to 0} P_h^{\pi} = 1$$

, we applied de l'Hôpital rule and obtained:

$$\lim_{\rho \to 0} \frac{p(1 - \frac{1}{P_h^{\pi}})}{\rho} \overset{H}{=} \lim_{\rho \to 0} \frac{p(\sum_{i=0}^{h-1} (p+1)^i + 2\rho((p+1)^3 + \dots + 3\rho^2((p+1)^6 + \dots)}{(P_h^{\pi})^2} = m - 1. \quad \Box$$

A similar conclusion can be drawn as in the star interconnection and as for a binomial tree under NLF strategy. In binomial trees spanned in homogeneous computer networks, under LLF strategy, when size V of the problem is big, and the problem is computationally intensive  $(\rho \to 0)$ , then the relative influence of the limited memory on the processing time is negligible.

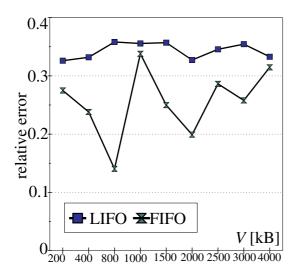

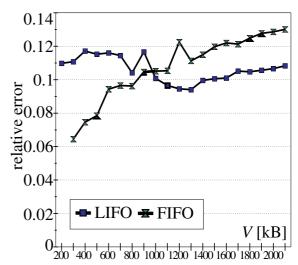

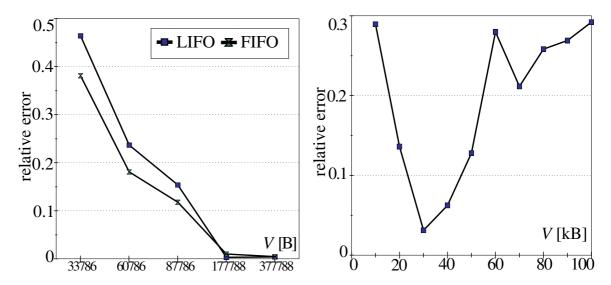

In our modeling of LLF strategy we observed several interesting facts:

- It was shown in [45] that LLF strategy is optimal in a system with unlimited memory. In the saturated system it is not, because LLF has greater number of communication startups than NLF. This communication overhead is not compensated for by a better distribution of the load and shorter computation time.

- In the earlier publications on divisible load theory [27, 45] systems with unlimited memory were considered (i.e. case 'inf'). Linear Programming formulations had more restricted form and e.g. inequality (3.14) had form of equation. As a result in LLF strategy, when volume V is small and the available memory is not restricted, only few layers can be activated (even if we have many processor layers) to satisfy the classical version of LP LLF. Thus, small increase of V may be satisfactory to activate more layers and in this way reduce schedule length. This is demonstrated in the example presented below. Consequently, with V increasing  $C_{max}^{inf}$  may decrease. This is evident in Fig. 3.5 where lines for 'inf' case and A = 1E-3, and A = 1 are not smooth for small V.

- The above irregular behavior was not observed in the LP NLF model.

- We observed that for  $A \approx C$  only the last layer was populated. When  $A \gg C$  the layers closer to the originator were more often populated.

- None of NLF, LLF strategies dominates the other in all cases. However, for big volumes and LLF shorter schedules were obtained.

**Example**. Consider a system with h=2, p=4, A=1E-3, C=1E-6, S=1E-3, V=20. In the system with unlimited memory [45] equations describing distribution of the load have positive solution only for one layer (5 processors altogether). Schedule length in this case is  $C_{max}^{sat} \approx 0.0048$ . However, when V=24 all 25 processors can

be activated, and  $C_{max}^{sat} \approx 0.003$ . Using LP LLF, and only the last layer we obtain  $C_{max} \approx 0.0029$  in the first, and  $C_{max} \approx 0.0031$ , in the second case.  $\square$

#### 3.2.3 Conclusions

In this section we analyzed divisible load distribution in systems with a single level of limited memory. Interconnection topologies of a star, and binomial tree under two different distribution strategies were studied. It appeared that in homogeneous systems and big computationally intensive applications mainly the processor and communication speeds limit performance of the systems. This conclusion is satisfied as long as the load fits into the available memory buffers and processing rates are constant for all assigned sizes of the load. For practical reasons these assumptions should be released. Such a relaxation is considered in chapter 4.

In our discussion we assumed that only the size of the receiver memory is restricting distribution of the load. The communication system is not limiting the size of the message. This may not be the case in practice. Therefore, a system with limited communication system capacity will be a subject of the further analysis in chapter 5.

In the next section we study the case of and arbitrary processor activation order.

## 3.3 Arbitrary activation sequence in star

In this section we address the problem of finding the optimal sequence of activating processors in a star network when memory buffers have limited sizes and communication delays include startup times. In the preceding discussion it was assumed that the sequence of activating processors is fixed. Here we relax this restriction and allow for selecting the best sequence of activating processors. This problem was raised in [53].

#### 3.3.1 Linear programming approach

In this section we formulate the problem of selecting the optimum processor activation order as a mathematical programming problem.

Let us denote by a binary variable  $x_{ij}$ , for i, j = 1, ..., m, the order of activating the processors.  $x_{ij} = 1$  denotes that  $P_j$  is activated on i-th position in the sequence. Otherwise  $x_{ij} = 0$ . The problem of optimal activation of the processors and distribution of the load can be formulated as a mixed nonlinear programming problem:

#### MNP:

minimize  $C_{max}$

subject to:

$$\alpha_0 A_0 V \le C_{max} \tag{3.18}$$

$$\sum_{k=1}^{i} \sum_{j=1}^{m} x_{kj} (\alpha_j V C_j + S_j) + \sum_{j=1}^{m} x_{ij} \alpha_j V A_j \ge C_{max} \quad \text{for } i = 1, \dots, m$$

(3.19)

$$\sum_{i=1}^{m} x_{ij} \le 1 \qquad \text{for } j = 1, \dots, m$$

(3.20)

$$\sum_{j=1}^{m} x_{ij} \le 1 \qquad \text{for } i = 1, \dots, m$$

(3.21)

$$x_{ij} \in \{0, 1\}$$

for  $i, j = 1, \dots, m$  (3.22)

$$\alpha_0 + \sum_{j=1}^m \sum_{i=1}^m x_{ij} \alpha_j = 1 \tag{3.23}$$

$$B_j \ge \alpha_j V \ge 0$$

for  $j = 0, \dots, m$  (3.24)

The above MNP formulation is a mixed problem because we have both binary variables  $x_{ij}$ , and continuous variables  $\alpha_i$ ,  $C_{max}$ . MNP is nonlinear because in constraints (3.19), (3.23) we have multiplication of the variables. Equations (3.18) and (3.19) demand that all processors finish computing before  $C_{max}$ . In inequalities (3.19) term  $\sum_{k=1}^{i} \sum_{j=1}^{m} x_{kj} (\alpha_j V C_j + S_j)$  is the time of sending the load to the processor activated as *i*-th in the sequence, and  $\sum_{j=1}^{m} x_{ij} A_j \alpha_j V$  is the computation time of the *i*-th

processor in the sequence. Constraints (3.20)-(3.22) guarantee that the sequence of activating the processors is correct: each PE is activated at most once by (3.20), each position in the activation sequence is occupied by at most one processor by (3.21). Due to weak form of the inequalities some processors may remain idle. Equation (3.23) guarantees processing of the whole load. Observe that some machines may be missing in the activation sequence, and  $x_{ij} = 0$  for i, j = 1, ..., m is a valid solution for constraints (3.20)-(3.22). Yet, it would not be a valid solution to our problem because appropriate communication time would not appear in equations (3.19). In order to prevent such a situation term  $\sum_{i=1}^{m} x_{ij}\alpha_j$  in equation (3.23) guarantees that only the chunks sent to the processors (i.e. with  $x_{ij} = 1$ ) are counted as really processed. Equations (3.24), guarantee that the load can be feasibly assigned to the processors. Let us apply the above formulation to solve Example 3 from [53].

**Example**. We have the same data as in the previous example: m = 4, V = 100,  $A_0 = 1, A_1 = 5, A_2 = 4, A_3 = 3, A_4 = 2, B_0 = 10, B_1 = 20, B_2 = 45, B_3 = 15, B_4 = 30, C_1 = 4, C_2 = 3, C_3 = 2, C_4 = 1, S_i = 0, \text{ for } i = 1, \dots, 4.$

| MS Excel ver. 7.0 managed to obtain the following solution to MNP | MS Exce | l ver.7.0 | managed | to obtain | the fo | ollowing | solution | to MNP: |

|-------------------------------------------------------------------|---------|-----------|---------|-----------|--------|----------|----------|---------|

|-------------------------------------------------------------------|---------|-----------|---------|-----------|--------|----------|----------|---------|

| processor | $B_i$ | $\alpha_i$ | communication               | computation       |

|-----------|-------|------------|-----------------------------|-------------------|

| order     |       |            | $\operatorname{completion}$ | ${ m completion}$ |

| $P_0$     | 10    | 10         | 0                           | 10                |

| $P_2$     | 45    | 35.2941    | 105.8824                    | 247.0588          |

| $P_4$     | 30    | 30         | 135.8824                    | 195.8824          |

| $P_1$     | 20    | 12.3529    | 185.2941                    | 247.0588          |

| $P_3$     | 15    | 12.3529    | 210                         | 247.0588          |

The sequence of activating the processors, according to the solver we used, is  $P_2$ ,  $P_4$ ,  $P_1$ ,  $P_3$ . Schedule length is  $C_{max} = 247.0588$ , and it is better than the one found in [53]. The reasons for this were given earlier: IBS strategy proposed in [53] is a heuristic, not an optimization algorithm. For the same instance with V = 50 (also considered in [53]) the following solution was obtained for MNP:

| processor | $B_i$ | $\alpha_i$ | communication     | computation |

|-----------|-------|------------|-------------------|-------------|

| order     |       |            | ${ m completion}$ | completion  |

| $P_0$     | 10    | 10         | 0                 | 10          |

| $P_4$     | 30    | 24.277     | 24.277            | 72.832      |

| $P_3$     | 15    | 9.711      | 43.699            | 72.832      |

| $P_2$     | 45    | 4.162      | 56.185            | 72.832      |

| $P_1$     | 20    | 1.850      | 63.584            | 72.832      |

Thus, the sequence found is  $P_4, P_3, P_2, P_1$ , and  $C_{max} = 72.832$ .  $\square$

The computational complexity of the general purpose mixed nonlinear solvers applied to MNP is high. These codes are capable of solving hard computational problems such as traveling salesman problem, quadratic assignment problem, and even more involved ones. It has been shown in Section 3.1 that the problem of scheduling divisible loads in a star network with limited processor memory buffers and communication startup times is NP-hard. According to the current state of knowledge [40] only algorithms with computational complexity growing exponentially with the size of the problem are known for this kind of problems. Thus, the codes finding optimal solutions of MNP have the worst-case execution time growing exponentially, e.g. with the number of binary variables  $x_{ij}$ . As exponential functions increase explosively with the value of the argument, exponential-time algorithms are in practice restricted to small instances of the solved problem. This leaves space for heuristic methods which find good solution fast, and this is the advantage of IBS strategy proposed in [53].

## 3.3.2 Branch and Bound algorithm

Let us note that for fixed sequence of processors activation MNP problem reduces to LP problem defined in section 3.2.1. Therefore it can be deduced that the difficulty of our problem consists in determining the set of processors to be activated and the sequence of the activation. An exact optimization algorithm can be based on an enumeration of all such sets and sequences.

The method of dividing the set of all processor activation sequences into subsets that are exhaustively searched and/or eliminated constitutes the branching scheme of a branch-and-bound (B&B) algorithm. A branch-and-bound algorithm implicitly builds a tree with all possible solutions. In our B&B algorithm no decision is taken in the root of the tree, and the set of processors to be activated is empty. The first level of the tree consists of solutions with only one processor:  $(P_1), (P_2), \ldots, (P_m)$ . Each partial solution  $(P_i)$  is a root of the subtree comprising solutions starting with the activation of  $P_i$ , for  $i=1,\ldots,m$ . The subsets of the solutions represented by the nodes of the first level are divided (branched) at level two, to represent solutions consisting of two processors. Hence,  $(P_i, P_j)$  for  $j \in \{1, \dots, m\} - \{i\}$  are successors of  $(P_i)$  for  $i=1,\ldots,m$ . At the third level  $(P_i,P_j,P_k)$  for  $k\in\{1,\ldots,m\}-\{i,j\}$  are successors of  $(P_i, P_j)$ . Thus, a level r solution  $(P_i, \ldots, P_k)$  has successors  $(P_i, \ldots, P_k, P_l)$  at level r+1 obtained by a concatenation of  $(P_i,\ldots,P_k)$  with processor  $P_l$  which has not been activated in sequence  $(P_i, \ldots, P_k)$ . The depth of the tree is at most m because no more than m processors can be activated. Note, that both the leaves of the tree and the internal nodes are potential solutions. The tree is searched in the depth-first order.

The second important component of B&B algorithm is bounding which allows for pruning search tree nodes representing subsets of solutions certainly not better than some known solution. For each node  $a = (P_i, \ldots, P_k)$  of the search tree a lower bound LB(a) on the schedule length of all the a's successors is calculated. This lower bound is compared with the length C of the best known solution. If  $C \leq LB(a)$ , then there is no hope that any successor of node (solution) a improves the best known solution. Therefore, successors of a are not considered any more. Value C is updated each time a better solution is found. Initially, the lower bound for node a was calculated as the optimum  $C_{max}$  in the linear program (3.1)-(3.4) assuming a processor activation sequence  $(P_i, \ldots, P_k, P_{id}^{|Z|}(Z))$ , where  $Z = \mathcal{P} - \{P_i, \ldots, P_k\}$  is the set of the processors not included in a, and symbol  $P_{id}^{|Z|}(Z)$  stands for a sequence of |Z| copies of an ideal processor  $P_{id}(Z)$ .  $P_{id}(Z)$  has all the best parameters of the processors in the set

Z. Hence,  $P_{id}(Z)$  has processing ratio  $A_{id} = \min_{P_l \in Z} \{A_l\}$ , communication link with communication rate  $C_{id} = \min_{P_l \in Z} \{C_l\}$ , and startup time  $S_{id} = \min_{P_l \in Z} \{S_l\}$ , memory buffer size is  $B_{id} = \max_{P_l \in Z} \{B_l\}$ .

Unfortunately, the lower bound calculated in this way has two disadvantages. Firstly, when communication delay is big it may happen that the whole volume Vof the load can be processed on only a few processors in shorter time than the time needed to activate all m processors, and our lower bound is not correct. Consider an example: V = 10, m = 20,  $A_i = 1$ ,  $C_i = 0$ ,  $S_i = 1$ ,  $B_i = 10$ , for i = 1, ..., m. The load may be processed by using only four processors in  $C_{max}^* = 5$  using distribution  $\alpha_1 = 4, \alpha_2 = 3, \alpha_3 = 2, \alpha_4 = 1$ . The time needed to activate all m = 20 processors is  $20 > C_{max}^*$ . Note that if all m processors were used then some of them would receive no load (in the example  $\alpha_l = 0$ , for  $l = 5, \ldots, m$ ). Thus, the solutions of the linear program (3.1)-(3.2) for sequence  $(P_i, \ldots, P_k, P_{id}^{|Z|}(Z))$  with  $\alpha_l = 0$ , for some l, indicate that the sequence is too long, and the lower bound is inaccurate. In other words, some processor  $P_l$  introduces a communication delay contributing to the schedule length, but does not compute. Therefore,  $P_l$  can be eliminated from the activation sequence without increasing the schedule length. We cannot remove, however, the real processors from sequence a. The second disadvantage of the above method appears when the ideal processor is superior to the real processors in the sequence a. Then, the real processors may, again, receive no load. Both situations, can be dealt with by decreasing the number of ideal processors until all processors in the sequence receive some load. For the above reasons the procedure of calculating the lower bound has been extended by iterative decreasing the number of ideal processors until all processors receive some load.

## 3.3.3 Heuristic algorithms

The problem of optimal scheduling divisible load in a heterogeneous star with communication startup times and limited memory sizes is computationally hard. The exact optimization algorithm presented in the previous section has exponential execution time int the worst case. Therefore, it is reasonable to consider heuristic algorithms as alternative methods of finding solutions to our problem. Heuristics, are low-order polynomial time algorithms providing feasible solutions. However, the solutions derived by them are not guaranteed to be optimal.

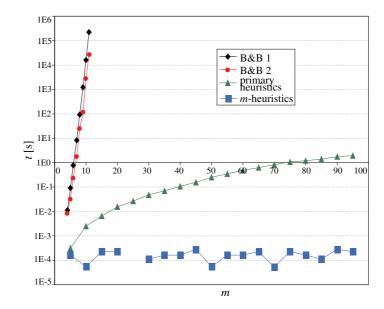

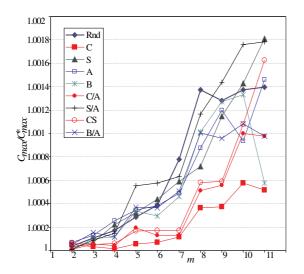

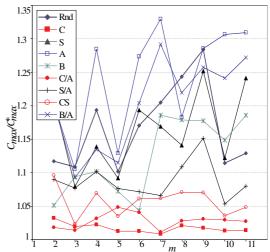

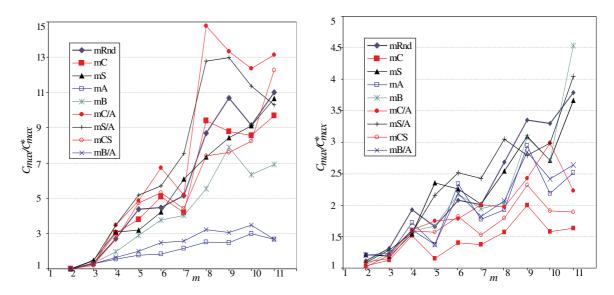

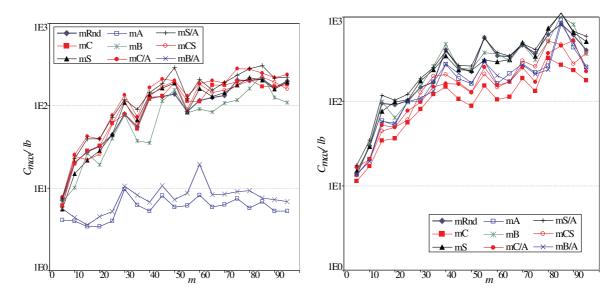

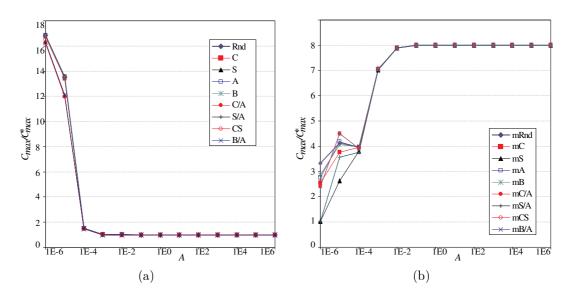

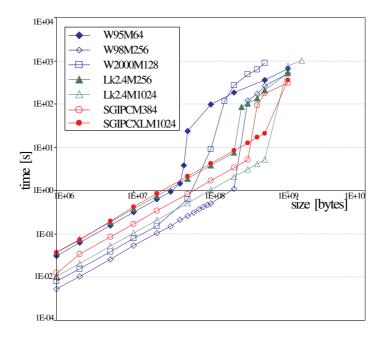

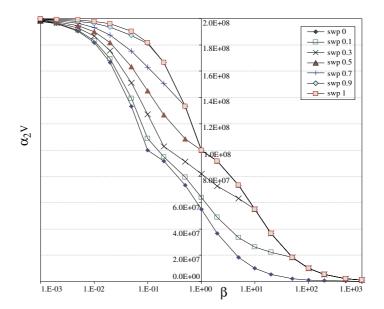

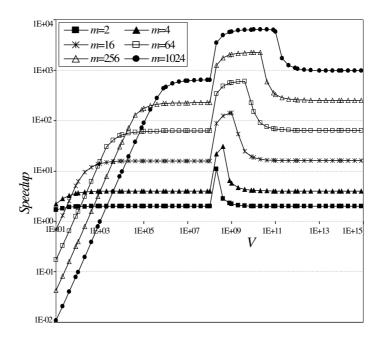

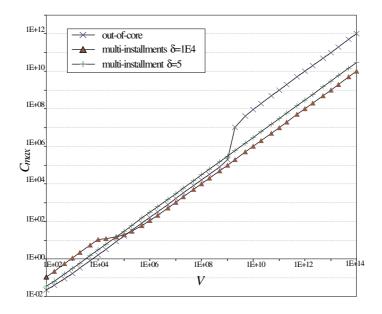

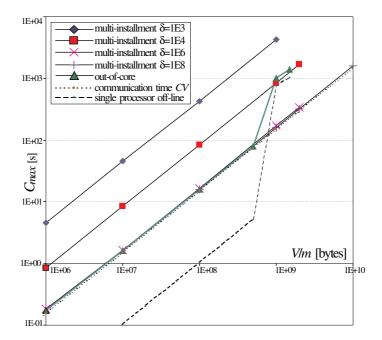

The heuristic methods we studied try to find the best sequence of processor activation, and the set of working processors. The first set of heuristics activates all available processors according to a single processor parameter. Then the distribution of the load (i.e.  $\alpha_i$ 's) is found using formulation (3.1)-(3.4). Thus, we studied heuristic A which ordered processors according to the nondecreasing value of processing rates (i.e.  $A_i$ 's). Analogously, heuristics C, and S were analyzed. Heuristic, B ordered processors according to nonincreasing value of buffer sizes B. The second set of heuristics intends to combine two parameters of processors. Heuristic C/A orders processors from the processor with the least value of  $\frac{C_i}{A_i}$  to the processor with the biggest one. Heuristic S/A, is formulated similarly. Heuristic SC orders processors according to the increasing value of  $S_iC_i$ . Analogously, method B/A orders processors according to the decreasing values of  $\frac{B_i}{A_i}$ . The above group of heuristics will be called primary heuristics.